多用途穩(wěn)壓集成電路測試儀的設計原理

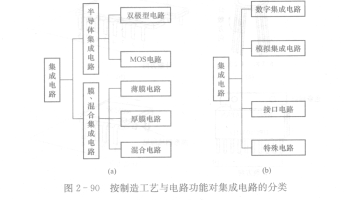

隨著電子技術的飛速發(fā)展,穩(wěn)壓集成電路在各種電子設備中扮演著至關重要的角色,從電源管理到信號處理,其性能直接影響系統(tǒng)的穩(wěn)定性和可靠性。因此,設計一種多用途穩(wěn)壓集成電路測試儀,能夠高效、準確地評估不同類型穩(wěn)壓IC的關鍵參數(shù),成為電子工程領域的重要需求。本文將深入探討多用途穩(wěn)壓集成電路測試儀的設計原理,涵蓋其核心功能、硬件架構、軟件控制以及測試流程,并結合集成電路設計的基本概念,解析如何實現(xiàn)儀器的通用性和精確性。

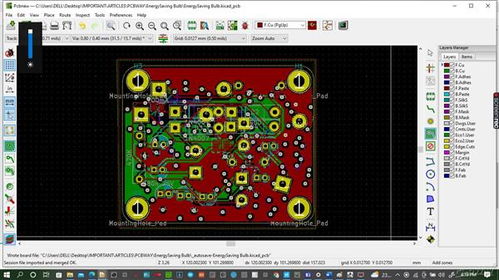

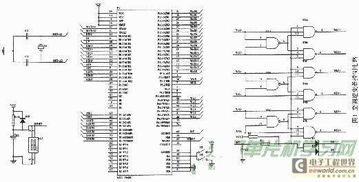

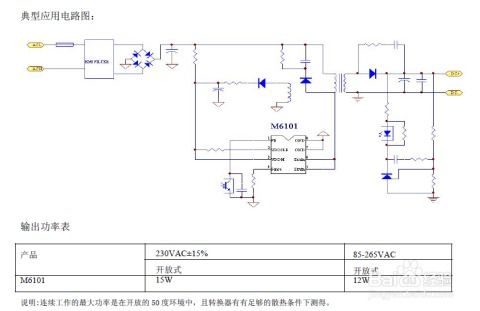

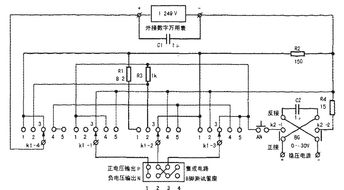

多用途穩(wěn)壓集成電路測試儀的核心設計目標是支持多種穩(wěn)壓IC的測試,如線性穩(wěn)壓器、開關穩(wěn)壓器等。其設計原理基于對穩(wěn)壓IC關鍵參數(shù)的全面測量,包括輸出電壓精度、負載調整率、線性調整率、紋波抑制比、溫度穩(wěn)定性以及效率等。為實現(xiàn)這一目標,測試儀通常采用模塊化硬件架構,包括可編程電源模塊、精密負載模塊、信號采集模塊和主控單元。可編程電源模塊負責提供可調的輸入電壓,模擬實際工作條件;精密負載模塊通過電子負載或電阻網(wǎng)絡,施加不同電流負載以測試IC的負載特性;信號采集模塊則利用高精度ADC(模數(shù)轉換器)實時監(jiān)測輸出電壓和電流,確保數(shù)據(jù)準確性。主控單元通常基于微處理器或FPGA,負責協(xié)調各模塊工作,處理數(shù)據(jù)并執(zhí)行測試算法。

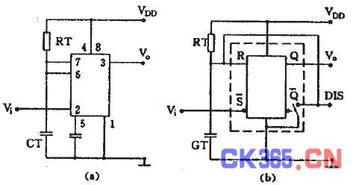

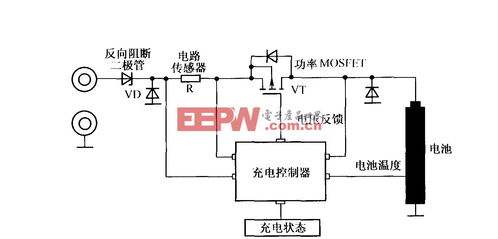

在集成電路設計方面,測試儀的設計需充分考慮被測IC的內部結構和工作原理。穩(wěn)壓集成電路的核心通常包括基準電壓源、誤差放大器、反饋網(wǎng)絡和功率器件。測試儀通過模擬反饋環(huán)路的開環(huán)和閉環(huán)條件,評估IC的穩(wěn)定性和瞬態(tài)響應。例如,在測試線性穩(wěn)壓器時,測試儀會注入小信號擾動,觀察輸出電壓的恢復時間,以判斷其動態(tài)性能。對于開關穩(wěn)壓器,測試儀需測量開關頻率、占空比和效率,這要求硬件支持高頻信號采集和分析。集成電路設計的趨勢是向小型化、低功耗和高集成度發(fā)展,因此測試儀的設計也需適應這些特點,例如通過集成溫度傳感器來測試IC的熱性能,或使用數(shù)字接口(如I2C、SPI)與智能穩(wěn)壓IC通信,實現(xiàn)參數(shù)配置和狀態(tài)監(jiān)控。

軟件控制是多用途測試儀的另一關鍵部分。用戶通過圖形界面或腳本輸入測試參數(shù),軟件根據(jù)預設算法控制硬件執(zhí)行測試序列。例如,在測試負載調整率時,軟件會逐步增加負載電流,同時記錄輸出電壓變化,計算調整率。為提高測試效率,軟件通常支持自動化批量測試和數(shù)據(jù)記錄,并可生成詳細報告。在集成電路設計優(yōu)化中,測試數(shù)據(jù)可用于反饋設計改進,例如通過分析紋波數(shù)據(jù)來優(yōu)化濾波電路布局。

測試流程的設計需遵循標準化原則,以確保結果的可比性和重復性。典型流程包括:初始化設置(如輸入電壓范圍、負載條件)、執(zhí)行靜態(tài)測試(測量直流參數(shù))、動態(tài)測試(評估瞬態(tài)響應)以及環(huán)境測試(如溫度變化下的性能)。在設計測試儀時,必須考慮校準機制,定期使用標準器件進行校準,以消除系統(tǒng)誤差。

多用途穩(wěn)壓集成電路測試儀的設計原理融合了電子測量技術、集成電路理論和自動化控制,其成功實現(xiàn)依賴于精密的硬件設計、靈活的軟件算法以及對被測IC工作原理的深入理解。隨著集成電路技術的不斷演進,測試儀的設計也將持續(xù)優(yōu)化,支持更復雜的穩(wěn)壓方案,如多相穩(wěn)壓器和數(shù)字電源管理IC,為電子行業(yè)提供可靠的測試保障。

如若轉載,請注明出處:http://www.blrsj.cn/product/42.html

更新時間:2026-03-15 03:46:36